AMD Power Design Manager 2025.1現(xiàn)已推出

AMD Power Design Manager 2025.1 版(PDM)現(xiàn)已推出——增加了對第二....

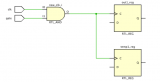

AMD FPGA異步模式與同步模式的對比

本文講述了AMD UltraScale /UltraScale+ FPGA 原生模式下,異步模式與同....

全新AMD Vitis統(tǒng)一軟件平臺2025.1版本發(fā)布

全新 AMD Vitis 統(tǒng)一軟件平臺 2025.1 版正式上線!此最新版本為使用 AMD Vers....

AMD Vivado Design Suite 2025.1現(xiàn)已推出

AMD Vivado Design Suite 2025.1 現(xiàn)已推出,支持 AMD Spartan....

利用AMD VERSAL自適應(yīng)SoC的設(shè)計基線策略

您是否準(zhǔn)備將設(shè)計遷移到 AMD Versal 自適應(yīng) SoC?設(shè)計基線是一種行之有效的時序收斂方法,....

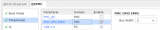

AMD Versal Adaptive SoC Clock Wizard AXI DRP示例

本文將使用 Clocking Wizard 文檔 PG321 中的“通過 AXI4-Lite 進(jìn)行動....

如何使用One Spin檢查AMD Vivado Design Suite Synth的結(jié)果

本文講述了如何使用 One Spin 檢查 AMD Vivado Design Suite Synt....

AMD Vivado Design Tool綜合中的門控時鐘轉(zhuǎn)換

傳統(tǒng)上,使用門控時鐘是 ASIC 設(shè)計中降低系統(tǒng)功耗的常見方法。通過門控時鐘,可在非必要時阻止整組寄....

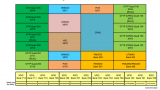

AMD Versal自適應(yīng)SoC器件Advanced Flow概覽(上)

在最新發(fā)布的 AMD Vivado Design Suite 2024.2 中,引入的新特性之一是啟....

AMD Versal自適應(yīng)SoC DDRMC如何使用Micron仿真模型進(jìn)行仿真

AMD Versal 自適應(yīng) SoC 器件上 DDR4 硬核控制器 DDRMC 跑仿真時,按照 IP....

如何在同一塊開發(fā)板上測試GT遠(yuǎn)端環(huán)回

環(huán)回(loopback)是 GT 的一種特殊配置模式??梢园寻l(fā)送端的數(shù)據(jù)直通過自身 PMA 層或?qū)Ψ?...

如何通過PMC_GPIO喚醒AMD Versal? Adaptive SoC Linux系統(tǒng)

在功耗敏感的系統(tǒng)里,我們通常會在系統(tǒng)空閑的時候?qū)⑾到y(tǒng)休眠,然后可以通過一些外設(shè)的輸入來喚醒系統(tǒng),比如....

CPM PCIE做RC時如何完成對復(fù)位信號的控制

PCI Express 是一種即插即用協(xié)議,主機(jī)在啟動時將枚舉 PCIe 設(shè)備。此過程包括主機(jī)從讀....

AMD Vitis Unified Software Platform 2024.2發(fā)布

近日,全新 AMD Vitis Unified Software Platform 2024.2 版....

AMD Vivado Design Suite 2024.2全新推出

AMD Vivado Design Suite 2024.2 全新推出,使用 AMD Versal ....

AMD Alveo V80計算加速器網(wǎng)絡(luò)研討會

歡迎參加本次網(wǎng)絡(luò)研討會,我們將深入探討 AMD Alveo V80 計算加速器如何幫助您處理高性能計....

AMD第二代Versal自適應(yīng)SoC的主要特色

AMD 第二代 AMD Versal AI Edge 和 Versal Prime 系列助力 AI ....