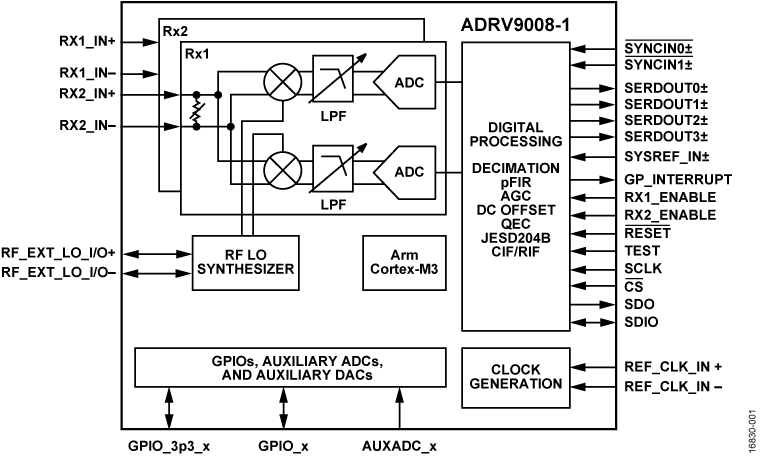

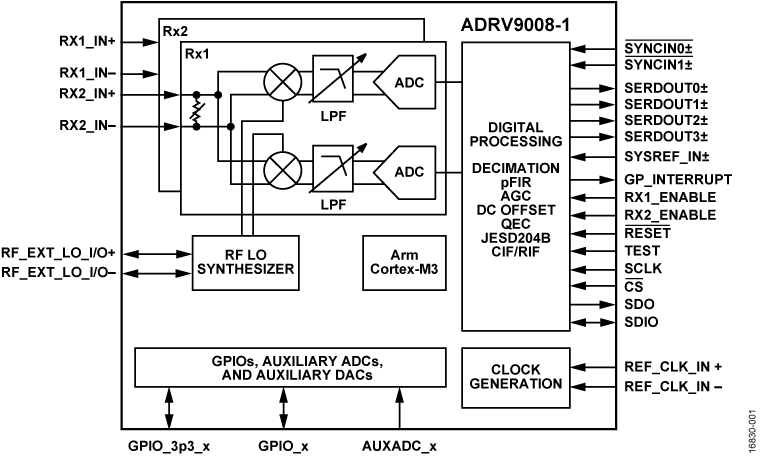

ADRV9008-1 集成式雙射頻接收器

數(shù)據(jù):

ADRV9008-1產(chǎn)品技術(shù)英文資料手冊

優(yōu)勢和特點

- 雙接收器

- 最大接收器帶寬:200 MHz

- 全集成的小數(shù) N 射頻合成器

- 全集成的時鐘合成器

- 適用于射頻 LO 和基帶時鐘的多芯片相位同步

- JESD204B 數(shù)據(jù)路徑接口

- 調(diào)諧范圍:75 MHz 至 6000 MHz

產(chǎn)品詳情

接收路徑包括兩個獨立的具有一流動態(tài)范圍的寬帶 直接轉(zhuǎn)換接收器��。完整的接收子系統(tǒng)包括自動和手動衰減控制���、直流失調(diào)矯正�����、正交誤差校正 (QEC) 以及數(shù)字濾波���,因此數(shù)字基帶中不再需要這些功能���。它集成了射頻前端控制以及適用于功率放大器 (PA) 的模數(shù)轉(zhuǎn)換器 (ADC)、數(shù)模轉(zhuǎn)換器 (DAC) 和通用輸入/輸出 (GPIO) 等若干輔助功能��。

除了自動增益控制 (AGC) 外���,ADRV9008-1 還具有靈活的外部增益控制模式���,可在動態(tài)設(shè)置系統(tǒng)級增益的過程中實現(xiàn)出色的靈活性。

接收的信號通過一組四個高動態(tài)范圍連續(xù)時間 Σ-Δ ADC 進行數(shù)字化處理��,這些 ADC 具有固有的抗混疊特性��。組合直接轉(zhuǎn)換架構(gòu)不受帶外鏡像混合影響�����,由于不存在混疊����,因而與傳統(tǒng)中頻 (IF) 接收器相比,放寬了 RF 濾波器的要求�。

完全集成的鎖相環(huán) (PLL) 為接收器信號路徑提供高性能、低功耗小數(shù) N 射頻合成�。一個額外的合成器生成轉(zhuǎn)換器、數(shù)字電路和串行接口所需的時鐘���。多芯片同步機制可在多個 ADRV9008-1 芯片之間同步射頻本地振蕩器 (LO) 的相位和基帶時鐘��。已經(jīng)采取預(yù)防措施以提供高性能基站應(yīng)用所要求的隔離��。集成了所有壓控振蕩器 (VCO) 和環(huán)路濾波器元件

高速 JESD204B 接口支持高達 12.288 Gbps 的線速�,因此在最寬帶寬模式下�,每個發(fā)射器有兩個線路,每個接收器有一個線路��。此接口還支持適用于較低帶寬的交錯模式����,將高速數(shù)據(jù)接口總線數(shù)減少到了一個。支持固定和浮點數(shù)據(jù)格式���。浮點格式可使內(nèi)部 AGC 對解調(diào)器器件不可見���。

ADRV9008-1 的內(nèi)核可以直接由 1.3 V 和 1.8 V 穩(wěn)壓器供電�,并通過標準 4 線串行端口進行控制�。包括了全面的節(jié)電模式,以便在正常使用過程中最大限度地減小功耗����。ADRV9008-1 采用 12 mm × 12 mm、196 球芯片級球柵陣列 (CSP_BGA) 封裝���。

應(yīng)用

- 3G���、4G 和 5G FDD 宏蜂窩基站

- 寬帶有源天線系統(tǒng)

- 大規(guī)模多輸入多輸出 (MIMO)

- 相控陣雷達

- 電子戰(zhàn)

- 軍事通信

- 便攜測試設(shè)備

方框圖