8.1System Generator的特點(diǎn)與安裝

8.1.1System Generator的主要特點(diǎn)

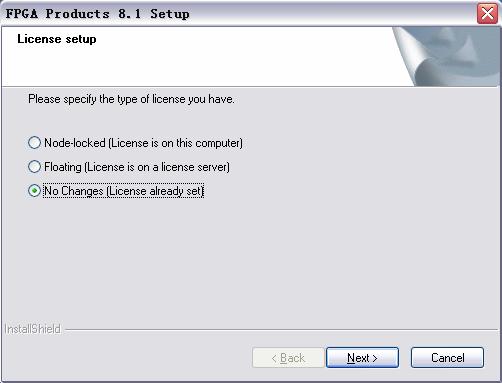

8.1.2System Generator的安裝和配置

8.2System Generator的使用基礎(chǔ)

8.2.1System Generator開發(fā)流程

8.2.2Simulink的應(yīng)用

8.3基于System Generator的DSP系統(tǒng)設(shè)計(jì)

8.3.1System Generator的應(yīng)用

8.3.2System Generator中的信號(hào)類型

8.3.3自動(dòng)代碼生成

8.3.4編譯MATLAB設(shè)計(jì)生成FPGA代碼

8.3.5子系統(tǒng)的建立與ISE調(diào)用

8.4基于System Generator的硬件協(xié)仿真

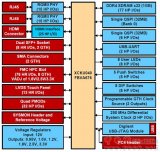

8.4.1硬件協(xié)仿真平臺(tái)的特點(diǎn)與平臺(tái)安裝

8.4.2硬件協(xié)仿真的基本操作

8.4.3共享存儲(chǔ)器的操作

8.5System Generator的高級(jí)應(yīng)用

8.5.1導(dǎo)入外部的HDL程序模塊

8.5.2設(shè)計(jì)在線調(diào)試

8.5.3系統(tǒng)中的多時(shí)鐘設(shè)計(jì)

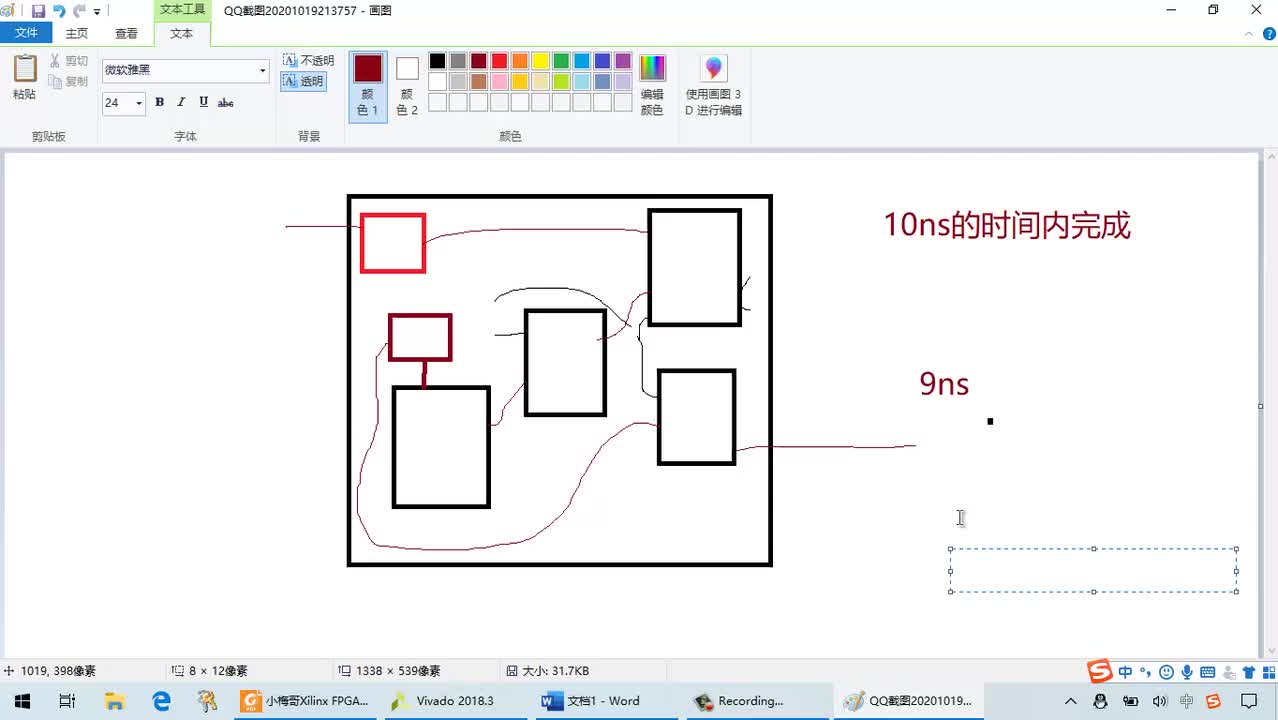

8.5.4FPGA設(shè)計(jì)的高級(jí)技巧

本章小結(jié)

第9章數(shù)字信號(hào)處理專題

9.1數(shù)字信號(hào)

9.1.1數(shù)字信號(hào)的產(chǎn)生

9.1.2采樣定理

9.1.3數(shù)字系統(tǒng)的主要性能指標(biāo)

9.1.4A/D轉(zhuǎn)換的字長效應(yīng)

9.2常用DSP IP Core及其應(yīng)用

9.2.1DDS模塊IP Core的應(yīng)用

9.2.2FFT算法IP Core的應(yīng)用

9.2.3Cordic算法IP Core的應(yīng)用

9.2.4FIR濾波器IP Core的應(yīng)用

9.3多速率濾波器的FPGA實(shí)現(xiàn)

9.3.1多速率信號(hào)處理的意義

9.3.2多速率信號(hào)濾波器的基本操作

9.3.3CIC濾波器的FPGA實(shí)現(xiàn)

9.3.4HB濾波器的FPGA實(shí)現(xiàn)

本章小結(jié)

第10章SERDES技術(shù)專題

10.1高速數(shù)據(jù)連接功能

10.1.1高速數(shù)據(jù)傳輸

10.1.2Xilinx公司高速連接功能的解決方案

10.2實(shí)現(xiàn)吉比特高速串行I/O的相關(guān)技術(shù)

10.2.1吉比特高速串行I/O的特點(diǎn)和應(yīng)用

10.2.2吉比特串行I/O系統(tǒng)的組成

10.2.3吉比特串行I/O的設(shè)計(jì)要點(diǎn)

10.3Rocket I/O收發(fā)器原理與開發(fā)

10.3.1Rocket I/O硬核組成與工作原理

10.3.2GTP硬核組成與工作原理

10.3.3GTP Wizard開發(fā)實(shí)例

10.4PCI?Express G1端點(diǎn)接口設(shè)計(jì)

10.4.1PCI Express G1技術(shù)

10.4.2Xilinx PCI Express G1端點(diǎn)模塊

10.4.3PCI Express G1端點(diǎn)接口實(shí)例解讀

本章小結(jié)

參考文獻(xiàn)

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論