本文介紹了如何準(zhǔn)確地估算采樣時(shí)鐘抖動(dòng),以及如何計(jì)算正確的上下整合邊界��。

2012-04-01 10:19:38 1665

1665

本系列文章共有三部分��,第 1 部分重點(diǎn)介紹如何準(zhǔn)確地估算某個(gè)時(shí)鐘源的抖動(dòng),以及如何將其與 ADC 的孔徑抖動(dòng)組合�。在第 2 部分中,該組合 抖動(dòng) 將用于計(jì)算 ADC 的 SRN����,然后將其與實(shí)際

2012-05-07 11:37:30 2668

2668

為了正確理解時(shí)鐘相關(guān)器件的抖動(dòng)指標(biāo)規(guī)格�,同時(shí)選擇抖動(dòng)性能適合系統(tǒng)應(yīng)用的時(shí)鐘解決方案��,本文詳細(xì)介紹了如何理解兩種類(lèi)型時(shí)鐘驅(qū)動(dòng)器的抖動(dòng)參數(shù)�,以及從鎖相環(huán)輸出噪聲特性理解時(shí)鐘器件作為合成器�、抖動(dòng)濾除功能時(shí)的噪聲特性���。

2013-06-21 15:40:41 14342

14342

-Si539x時(shí)鐘提升頻率靈活性和抖動(dòng)性能--Si56x Ultra Series? XO/VCXO提供最大可達(dá)3GHz的任意頻率時(shí)鐘-。

2018-06-26 15:19:41 7075

7075 今天我們將討論時(shí)鐘如何影響精密 ADC�,涉及時(shí)鐘抖動(dòng)��、時(shí)鐘互調(diào)和時(shí)鐘的最佳 PCB 布局實(shí)踐����。

2023-04-11 09:13:22 645

645 時(shí)鐘抖動(dòng)技術(shù)適合于各種周期性的脈沖信號(hào)����,典型的是電力電子設(shè)備中的PWM電壓和數(shù)字電路中的時(shí)鐘信號(hào)�����。

2023-09-11 10:55:34 503

503

時(shí)鐘抖動(dòng)是相對(duì)于理想時(shí)鐘沿實(shí)際時(shí)鐘存在不隨時(shí)間積累的���、時(shí)而超前��、時(shí)而滯后的偏移稱為時(shí)鐘抖動(dòng),簡(jiǎn)稱抖動(dòng)

2023-11-08 15:08:01 892

892

Silicon Labs日前擴(kuò)展了Si539x抖動(dòng)衰減器系列產(chǎn)品���,其新器件型號(hào)具有完全集成的參考時(shí)鐘���、增強(qiáng)了系統(tǒng)可靠性和性能��,同時(shí)簡(jiǎn)化了高速網(wǎng)絡(luò)設(shè)計(jì)中的PCB布局布線�。

2019-06-20 16:16:56 4682

4682 的148.35 MHz進(jìn)入收發(fā)器的gtxe2_i(GTXE2_CHANNEL)�。這適用于SDI����。 LMH1983的27 MHZ時(shí)鐘進(jìn)入控制I2C總線的過(guò)程��,并從Si5324產(chǎn)生156.25 MHz時(shí)鐘

2020-05-11 08:09:08

BOARD EVALUATION SI5324

2023-03-29 22:53:25

SI5324-EVB��,SI5324評(píng)估板�,0.002至710 MHz時(shí)鐘發(fā)生器���。 SI5324-EVB為評(píng)估SI5316任意速率精度時(shí)鐘提供平臺(tái)。 SI5316直接使用器件上的配置引腳進(jìn)行控制

2019-02-22 09:30:51

Si5324 - Pin-Controlled 1_710 MHz Jitter Cleaning Clock - Silicon Laboratories

2022-11-04 17:22:44

嗨����,Si5324已用于Xilinx參考設(shè)計(jì)(KC705評(píng)估板)�,可為10 gig SFP生成時(shí)鐘。https://www.xilinx.com/support/documentation

2020-05-12 09:20:29

在本文中��,我們將討論抖動(dòng)傳遞及其性能��,以及相位噪聲測(cè)量技術(shù)的局限性�����。 時(shí)鐘抖動(dòng)和邊沿速率 圖1顯示了由一個(gè)通用公式表述的三種波形。該公式包括相位噪聲項(xiàng)“φ(t)”和幅度噪聲項(xiàng)“λ(t)����。對(duì)評(píng)估的三個(gè)

2022-11-23 07:59:49

如題����,目前項(xiàng)目要做一個(gè)100m16bit的數(shù)據(jù)采集卡,看了下貴公司的AD9460�,但是差分參考時(shí)鐘無(wú)法選擇��?

需不需要加一個(gè)時(shí)鐘綜合芯片比如Si5324����?但類(lèi)似的這種芯片市場(chǎng)上很不好買(mǎi)到�����。

如果用elcosc能否推薦個(gè)廠家和芯片�����?還有ad9460能否申請(qǐng)樣品?謝謝

2023-12-25 07:44:39

如題�,目前項(xiàng)目要做一個(gè)100m16bit的數(shù)據(jù)采集卡���,看了下貴公司的AD9460,但是差分參考時(shí)鐘無(wú)法選擇����?需不需要加一個(gè)時(shí)鐘綜合芯片比如Si5324�����?但類(lèi)似的這種芯片市場(chǎng)上很不好買(mǎi)到����。如果用elcosc能否推薦個(gè)廠家和芯片�?還有ad9460能否申請(qǐng)樣品?謝謝

2018-11-28 09:24:25

ZC706開(kāi)發(fā)板上的SI5324需要通過(guò)I2C配置����,官網(wǎng)找了一圈�����,只有VC709和KC705的例程���,都是基于MICROBLAZE的�,改到ZC706上問(wèn)題也不大���,準(zhǔn)備動(dòng)手這際�,轉(zhuǎn)念一想�����,何不

2019-07-05 08:22:37

C138和C141之后測(cè)量信號(hào)的差異��。不幸的是,我沒(méi)有在Si5324的引腳29和28上看到任何時(shí)鐘輸出��,在衰減抖動(dòng)之后��,應(yīng)該將我的125 MHz反饋回FPGA和SFP IP。我的設(shè)計(jì)很簡(jiǎn)單���。它由1G eth

2019-09-27 09:21:26

MHz的雙時(shí)鐘輸入,并產(chǎn)生兩個(gè)相等的倍頻時(shí)鐘輸出����,范圍為8 kHz至644.53 MHz�����。輸入時(shí)鐘頻率和時(shí)鐘倍頻比可從流行的SyncE和T1 / E1速率表中選擇���。 Si5315基于第三代DSPLL技術(shù),可在高度集成的PLL解決方案中提供任意速率頻率合成和抖動(dòng)衰減���,無(wú)需外部VCXO和環(huán)路濾波器組件

2019-02-26 09:34:20

各種抖動(dòng)技術(shù)規(guī)范是什么抖動(dòng)的影響有哪些

2021-04-06 09:22:00

Si5328-EVB��,評(píng)估套件為評(píng)估Si5328任意頻率精密時(shí)鐘定時(shí)IC提供了一個(gè)平臺(tái)����。 Si5328由微處理器或MCU(微控制器單元)通過(guò)I2C或SPI接口控制。 Si5328是一款抖動(dòng)衰減器

2019-01-30 15:30:20

SI5340-D-EVB�����,評(píng)估板用于評(píng)估Si5340任意頻率��,任意輸出,抖動(dòng)衰減時(shí)鐘倍頻器版本D.器件版本以白色1英寸x 0.187英寸標(biāo)簽與文本SI5340-D區(qū)分-EB安裝在主板的左下角�����。 (僅用于訂購(gòu)目的��,術(shù)語(yǔ)EB和EVB分別指板和套件

2019-02-26 09:33:59

SI5340-EVB,評(píng)估板用于評(píng)估Si5340低抖動(dòng)任意頻率時(shí)鐘發(fā)生器�����。 Si5340采用獲得專利的Multisynth技術(shù)�,可產(chǎn)生多達(dá)10個(gè)獨(dú)立時(shí)鐘頻率���,每個(gè)頻率具有0 ppm的合成誤差

2019-02-26 09:28:56

SI5341-D-EVB�,評(píng)估板用于評(píng)估Si5341任意頻率��,任意輸出��,抖動(dòng)衰減時(shí)鐘倍頻器版本D.器件版本以白色1英寸x 0.187英寸標(biāo)簽與文本SI5341-D區(qū)分-EB安裝在主板的左下角。 (僅用于訂購(gòu)目的��,術(shù)語(yǔ)EB和EVB分別指板和套件

2019-02-26 09:41:06

SI5341-EVB�����,評(píng)估板用于評(píng)估Si5341低抖動(dòng)任意頻率時(shí)鐘發(fā)生器。 Si5341采用獲得專利的Multisynth技術(shù)�����,可產(chǎn)生多達(dá)10個(gè)獨(dú)立時(shí)鐘頻率��,每個(gè)頻率具有0 ppm的合成誤差

2019-02-25 07:03:01

SI5342-D-EVB,評(píng)估板用于評(píng)估Si5342任意頻率�����,任意輸出�����,抖動(dòng)衰減時(shí)鐘倍頻器版本D.器件版本以白色1英寸x 0.187英寸標(biāo)簽與文本SI5342-D區(qū)分-EB安裝在主板的左下角。 (僅用于訂購(gòu)目的����,術(shù)語(yǔ)EB和EVB分別指板和套件

2019-02-25 09:42:36

SI5344-D-EVB���,基于Si5344任意頻率����,任意輸出��,抖動(dòng)衰減時(shí)鐘倍頻器Rev.D的評(píng)估板

2019-02-25 06:21:54

SI5344-EVB,評(píng)估板用于評(píng)估Si5344任意頻率����,任意輸出����,抖動(dòng)衰減時(shí)鐘倍頻器��。 Si5344結(jié)合了第四代DSPLL和Multisynth技術(shù)�,可為需要最高抖動(dòng)性能的應(yīng)用提供任意頻率時(shí)鐘

2019-02-26 09:36:27

SI5345-D-EVB��,評(píng)估板用于評(píng)估Si5345任意頻率�,任意輸出��,抖動(dòng)衰減時(shí)鐘倍頻器版本D.器件版本以白色1英寸x 0.187英寸標(biāo)簽與文本SI5345-D區(qū)分-EB安裝在主板的左下角�。 (僅用于訂購(gòu)目的,術(shù)語(yǔ)EB和EVB分別指板和套件

2019-02-25 09:46:14

SI5345-EVB���,評(píng)估板用于評(píng)估Si5345任意頻率�����,任意輸出,抖動(dòng)衰減時(shí)鐘倍頻器��。 Si5345結(jié)合了第四代DSPLL和Multisynth技術(shù)����,可為需要最高抖動(dòng)性能的應(yīng)用生成任意頻率時(shí)鐘

2019-02-26 07:34:30

SI5346-D-EVB���,評(píng)估板用于評(píng)估Si5346任意頻率,任意輸出��,抖動(dòng)衰減時(shí)鐘倍頻器版本D.器件版本以白色1英寸x 0.187英寸標(biāo)簽與文本SI5346-D區(qū)分-EB安裝在主板的左下角��。 (僅用于訂購(gòu)目的,術(shù)語(yǔ)EB和EVB分別指板和套件

2019-02-25 09:51:02

具有可編程的抖動(dòng)衰減帶寬�。 SI5348-D-EVB通過(guò)板載SMA連接器支持三個(gè)獨(dú)立的差分輸入時(shí)鐘��,兩個(gè)獨(dú)立的CMOS輸入時(shí)鐘和七個(gè)獨(dú)立的輸出時(shí)鐘���。 Si5348-D-EVB可以通過(guò)USB連接控制

2019-02-25 09:56:55

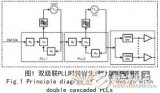

本文針對(duì)全方位的信號(hào)路徑系統(tǒng)中的高速全差分運(yùn)放及高頻寬14位模擬/數(shù)字轉(zhuǎn)換器的隨機(jī)及固定時(shí)鐘抖動(dòng),具體分析�����、研究了超低噪聲兼時(shí)鐘抖動(dòng)濾除技術(shù)�。研究選用雙級(jí)聯(lián)PLLatinum架構(gòu)�,配置高性能壓控振蕩器(VCXO)�,很好地實(shí)現(xiàn)了降噪和時(shí)鐘抖動(dòng)濾除的作用��。

2019-07-05 07:47:46

板上沒(méi)有此頻率的輸入�����。我主要看兩個(gè)選擇: - 通過(guò)FPGA內(nèi)的MMCM生成這個(gè)時(shí)鐘(我讀過(guò)它不是個(gè)好主意) - 使用電路板上的SI5324抖動(dòng)衰減器產(chǎn)生312.5MHZ頻率在kc705的原理圖中�,我

2019-09-27 09:51:28

��。振蕩器連接到引腳AK34和AL34(振蕩器具有差分輸出)���。3.我需要將引腳AK34和AL34(156,25MHz振蕩器)連接到引腳AW32和AW33(輸入到抖動(dòng)衰減器Si5324)。在這里我遇到了第一個(gè)

2019-09-25 11:45:13

你好;我正在使用VC709評(píng)估板。我想使用SI5324作為抖動(dòng)衰減器����。我使用DSPLLsim軟件計(jì)算SI5324寄存器值���。我想要的時(shí)鐘是122.88MHz,但Si5324產(chǎn)生119.4 MHz��。我

2019-10-18 09:36:35

theclock_control_program.vhd中有rom來(lái)存儲(chǔ)配置si5324的程序,而si5324_clock_setup.psm是定義了si5324寄存器值的代碼�。我想知道在更改寄存器值insi5324_clock_setup.psm后如何獲得newclock_control_program.vhd / .v�����。謝謝�。

2019-09-26 10:32:19

在下小白一枚��,花了一個(gè)多月的時(shí)間用FPGA控制SI5324C實(shí)現(xiàn)了時(shí)鐘的分頻,輸入50M輸出25M�,當(dāng)然了��,這用MMCM或者PLL也能實(shí)現(xiàn)����,但是SI5324C有一些特別的好處�����。程序在附件里

2017-11-24 20:31:36

Si539x芯片配置步驟第一次寫(xiě)博客(學(xué)習(xí)筆記),同時(shí)記錄一次Si5394時(shí)鐘芯片的配置����,寫(xiě)這個(gè)教程的原因也是因?yàn)樽约涸诰W(wǎng)上搜資料的時(shí)候,用的人少之又少�,讓后面用到的人少走些彎路吧�。前3點(diǎn)為芯片

2021-12-08 07:54:06

SI5342-EVB�,評(píng)估板用于評(píng)估Si5342任意頻率���,任意輸出�����,抖動(dòng)衰減時(shí)鐘倍頻器。 Si5342結(jié)合了第四代DSPLL和Multisynth技術(shù)�����,可為需要最高抖動(dòng)性能的應(yīng)用生成任意頻率時(shí)鐘���。可以使用Clock Builder Pro(CB Pro)軟件工具控制和配置Si5342-EVB

2019-02-27 11:28:29

SI5346-EVB���,評(píng)估板用于評(píng)估Si5346任意頻率��,任意輸出,抖動(dòng)衰減時(shí)鐘倍頻器��。 Si5346在單個(gè)IC中包含2個(gè)獨(dú)立的DSPLL���,每個(gè)DSPLL具有可編程的抖動(dòng)衰減帶寬

2019-02-28 08:17:47

SI5347-EVB��,評(píng)估板用于評(píng)估Si5347四路任意頻率抖動(dòng)衰減時(shí)鐘倍頻器����。 Si5347在單個(gè)IC中包含4個(gè)獨(dú)立的DSPLL��,每個(gè)DSPLL具有可編程的抖動(dòng)衰減帶寬�。 Si5347-EVB通過(guò)

2019-02-27 11:19:26

一塊音視頻處理芯片輸出1080i的數(shù)據(jù)Data及其同步時(shí)鐘Clk,但是時(shí)鐘clk的抖動(dòng)很大�����,我該如何處理呢����?另外���,抖動(dòng)很大的時(shí)鐘源能否在后面接入一個(gè)模擬鎖相環(huán)降低時(shí)鐘的抖動(dòng)呢�����?

2018-11-12 09:12:43

時(shí)鐘抖動(dòng)或結(jié)束時(shí)鐘抖動(dòng)的最佳方法是什么�?

2021-03-17 07:04:07

我正在為clk_stm1~155.52MHz的SFP stm1輸入計(jì)時(shí)我的GTX�����,這是從Si570到Si5324再到GTX模塊我不確定這個(gè)clk的ppm����,它可能會(huì)關(guān)閉多少...... Si

2019-09-23 06:44:53

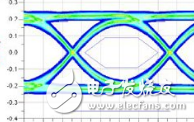

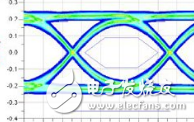

隨著數(shù)據(jù)速率的提高��,時(shí)鐘抖動(dòng)分析的需求也在與日俱增�。在高速串行數(shù)據(jù)鏈路中�����,時(shí)鐘抖動(dòng)會(huì)影響發(fā)射機(jī)、傳輸線和接收機(jī)的數(shù)據(jù)抖動(dòng)��。保證時(shí)鐘質(zhì)量的測(cè)量也在不斷發(fā)展

2008-12-27 12:24:05 6

6 隨著數(shù)據(jù)速率的提高��,時(shí)鐘抖動(dòng)分析的需求也在與日俱增����。在高速串行數(shù)據(jù)鏈路中���,時(shí)鐘抖動(dòng)會(huì)影響發(fā)射機(jī)���、傳輸線和接收機(jī)的數(shù)據(jù)抖動(dòng)。保證時(shí)鐘質(zhì)量的測(cè)量也在不斷發(fā)展����。目前

2009-07-07 14:01:21 20

20 本文主要討論采樣時(shí)鐘抖動(dòng)對(duì)ADC 信噪比性能的影響以及低抖動(dòng)采樣時(shí)鐘電路的設(shè)計(jì)���。

2009-11-27 11:24:07 15

15 MAX3625B是一款低抖動(dòng)�����、精密時(shí)鐘發(fā)生器�����,優(yōu)化用于網(wǎng)絡(luò)設(shè)備��。器件內(nèi)置晶體振蕩器和鎖相環(huán)(PLL)時(shí)鐘倍頻器���,以產(chǎn)生高頻時(shí)鐘輸出�,用于以太網(wǎng)、10G光纖通道及其它網(wǎng)絡(luò)設(shè)備��。Ma

2010-03-01 08:54:52 126

126 高速互聯(lián)鏈路中參考時(shí)鐘的抖動(dòng)分析與測(cè)量

在高速互聯(lián)鏈路中�,發(fā)送器的參考工作時(shí)鐘的抖動(dòng)是影響整個(gè)

2010-04-15 14:01:39 19

19 該應(yīng)用筆記提出了超低抖動(dòng)時(shí)鐘合成器的一種設(shè)計(jì)思路����,其目標(biāo)是產(chǎn)生2GHz時(shí)鐘時(shí)��,邊沿之間的抖動(dòng)< 100fs�����。分析和仿真結(jié)果表明,要達(dá)到這一抖動(dòng)指標(biāo)�,設(shè)計(jì)難度遠(yuǎn)遠(yuǎn)高于預(yù)期����。關(guān)

2009-04-21 23:14:05 723

723

摘要:該應(yīng)用筆記提出了超低抖動(dòng)時(shí)鐘合成器的一種設(shè)計(jì)思路�,其目標(biāo)是產(chǎn)生2GHz時(shí)鐘時(shí)�����,邊沿之間的抖動(dòng)< 100fs�����。分析和仿真結(jié)果表明����,要達(dá)到這一抖動(dòng)指標(biāo)����,設(shè)計(jì)難度遠(yuǎn)遠(yuǎn)高于預(yù)

2009-04-22 09:35:13 296

296

摘要:這是一篇關(guān)于時(shí)鐘(CLK)信號(hào)質(zhì)量的應(yīng)用筆記�,介紹如何測(cè)量抖動(dòng)和相位噪聲,包括周期抖動(dòng)����、逐周期抖動(dòng)和累加抖動(dòng)��。本文還描述了周期抖動(dòng)和相位噪聲譜之間的關(guān)系���,并介紹

2009-04-22 10:16:50 3736

3736

摘要:該應(yīng)用筆記提出了超低抖動(dòng)時(shí)鐘合成器的一種設(shè)計(jì)思路���,其目標(biāo)是產(chǎn)生2GHz時(shí)鐘時(shí)�����,邊沿之間的抖動(dòng)< 100fs。分析和仿真結(jié)果表明�����,要達(dá)到這一抖動(dòng)指標(biāo)�,設(shè)計(jì)難度遠(yuǎn)遠(yuǎn)高于預(yù)

2009-04-25 09:54:26 482

482

摘要:該應(yīng)用筆記提出了超低抖動(dòng)時(shí)鐘合成器的一種設(shè)計(jì)思路���,其目標(biāo)是產(chǎn)生2GHz時(shí)鐘時(shí)����,邊沿之間的抖動(dòng)< 100fs。分析和仿真結(jié)果表明�,要達(dá)到這一抖動(dòng)指標(biāo)��,設(shè)計(jì)難度遠(yuǎn)遠(yuǎn)高于預(yù)

2009-05-08 10:19:03 431

431

MAX3625A 低抖動(dòng)���、精密時(shí)鐘發(fā)生器,提供三路輸出

2009-08-13 13:01:27 828

828

MAX3624 低抖動(dòng)�、精密時(shí)鐘發(fā)生器����,提供四路輸出

概述

MAX3624是一款低抖動(dòng)精密

2009-09-18 08:56:41 682

682

理解不同類(lèi)型的時(shí)鐘抖動(dòng)

抖動(dòng)定義為信號(hào)距離其理想位置的偏離���。本文將重點(diǎn)研究時(shí)鐘抖動(dòng),并探討下面幾種類(lèi)型的時(shí)鐘抖動(dòng):相鄰周期抖動(dòng)����、周期抖動(dòng)�����、時(shí)間間隔誤

2010-01-06 11:48:11 1608

1608

MAX3625B 抖動(dòng)僅為0.36ps的PLL時(shí)鐘發(fā)生器

概述

MAX3625B是一款低抖動(dòng)���、精密時(shí)鐘發(fā)生器���,優(yōu)化用于網(wǎng)絡(luò)設(shè)備���。器件內(nèi)置晶體振蕩器和鎖相環(huán)(PLL)

2010-03-01 08:56:18 1345

1345

Si5374和Si5375是業(yè)界第一款集成了四個(gè)獨(dú)立高性能鎖相回路(PLL)的單芯片時(shí)鐘IC,它所提供的PLL集成是其它競(jìng)爭(zhēng)解決方案的兩倍��,抖動(dòng)則低了40%。

2011-05-18 09:39:47 2225

2225

時(shí)鐘抖動(dòng)時(shí)域分析(下):

2012-05-08 15:26:25 29

29 介紹 此應(yīng)用筆記側(cè)重于不同類(lèi)型的時(shí)鐘抖動(dòng)���。時(shí)鐘抖動(dòng)是從它的時(shí)鐘邊沿偏差理想的位置。了解時(shí)鐘抖動(dòng)非常重要在應(yīng)用中��,因?yàn)樗鹬P(guān)鍵作用��,在時(shí)間預(yù)算一個(gè)系統(tǒng)�。 隨著系統(tǒng)數(shù)據(jù)速率的增加����,定時(shí)抖動(dòng)成為關(guān)鍵

2017-04-01 16:13:18 6

6 時(shí)鐘抖動(dòng)時(shí)域分析�����,第 2 部分

2017-10-26 16:10:42 6

6 時(shí)鐘抖動(dòng)時(shí)域分析 第 3 部分

2017-10-26 16:13:28 4

4 時(shí)間域中分析的時(shí)鐘抖動(dòng)�����,第 1 部分

2017-10-26 16:16:23 4

4 隨著SERDES應(yīng)用越來(lái)越多,速率也越來(lái)越高�����,SI的問(wèn)題漸漸變得越來(lái)越重要�,它對(duì)PCB設(shè)計(jì)�,SERDES參數(shù)優(yōu)化都有著非常重要的指導(dǎo)作用����。而器件選型也往往以SI仿真開(kāi)始���。但是在仿真時(shí)���,工具會(huì)讓用戶

2017-11-18 13:17:01 4726

4726

本文針對(duì)全方位的信號(hào)路徑系統(tǒng)中的高速全差分運(yùn)放及高頻寬14位模擬/數(shù)字轉(zhuǎn)換器的隨機(jī)及固定時(shí)鐘抖動(dòng)���,具體分析���、研究了超低噪聲兼時(shí)鐘抖動(dòng)濾除技術(shù)。

2018-05-30 09:00:00 5165

5165

這些抖動(dòng)衰減時(shí)鐘倍增器結(jié)合了第四代DSPLL?和Multisynth?技術(shù)�����,為需要最高抖動(dòng)性能的應(yīng)用程序?qū)崿F(xiàn)任何頻率時(shí)鐘生成和抖動(dòng)衰減。這些設(shè)備可通過(guò)一個(gè)串行接口進(jìn)行編程����,該接口具有電路內(nèi)可編程

2019-07-01 08:00:00 20

20 的Multisynth?技術(shù)�����,可產(chǎn)生四個(gè)精度為0 ppm的獨(dú)立時(shí)鐘���。每個(gè)輸出時(shí)鐘可獨(dú)立配置,以支持各種信號(hào)格式和電源電壓�����。si5338在節(jié)省空間的4x 4 mm qfn封裝中提供低抖動(dòng)頻率合成����。該設(shè)備可通過(guò)與I2C/SMBus兼容的串行接口編程���,并支持1.8�、2.5或3.3V核心電源的操作�����。

2019-10-29 08:00:00 0

0 本文針對(duì)全方位的信號(hào)路徑系統(tǒng)中的高速全差分運(yùn)放及高頻寬14位模擬/數(shù)字轉(zhuǎn)換器的隨機(jī)及固定時(shí)鐘抖動(dòng),具體分析�、研究了超低噪聲兼時(shí)鐘抖動(dòng)濾除技術(shù)。研究選用雙級(jí)聯(lián)PLLatinum架構(gòu)�����,配置高性能壓控振蕩器(VCXO)����,很好地實(shí)現(xiàn)了降噪和時(shí)鐘抖動(dòng)濾除的作用����。

2020-09-23 10:45:00 2

2 電子發(fā)燒友網(wǎng)站提供《SI5324 時(shí)脈產(chǎn)生器參考設(shè)計(jì).pdf》資料免費(fèi)下載

2020-12-31 05:33:41 12

12 AD5324 Evaluation Software

2021-02-20 10:55:14 6

6 前言 :本文我們介紹下ADC采樣時(shí)鐘的抖動(dòng)(Jitter)參數(shù)對(duì)ADC采樣的影響��,主要介紹以下內(nèi)容: 時(shí)鐘抖動(dòng)的構(gòu)成 時(shí)鐘抖動(dòng)對(duì)ADC SNR的影響 如何計(jì)算時(shí)鐘抖動(dòng) 如何優(yōu)化時(shí)鐘抖動(dòng) 1.采樣理論

2021-04-07 16:43:45 7378

7378

AD5324評(píng)估軟件

2021-04-09 16:41:47 11

11 超低抖動(dòng)時(shí)鐘的產(chǎn)生與分配

2021-04-18 14:13:51 8

8 ADC時(shí)鐘接口中的最小抖動(dòng)

2021-05-09 12:19:40 6

6 AD5324評(píng)估軟件

2021-05-30 12:56:25 5

5 ADL5324 S參數(shù)

2021-06-11 10:11:58 1

1 電子發(fā)燒友網(wǎng)為你提供ADI(ti)EVAL-AD5324相關(guān)產(chǎn)品參數(shù)、數(shù)據(jù)手冊(cè)����,更有EVAL-AD5324的引腳圖���、接線圖��、封裝手冊(cè)、中文資料���、英文資料,EVAL-AD5324真值表��,EVAL-AD5324管腳等資料���,希望可以幫助到廣大的電子工程師們。

2021-08-17 00:00:04

Si539x芯片配置步驟第一次寫(xiě)博客(學(xué)習(xí)筆記)�����,同時(shí)記錄一次Si5394時(shí)鐘芯片的配置���,寫(xiě)這個(gè)教程的原因也是因?yàn)樽约涸诰W(wǎng)上搜資料的時(shí)候��,用的人少之又少,讓后面用到的人少走些彎路吧��。前3點(diǎn)為芯片

2021-11-25 20:21:03 18

18 KOYUELEC光與電子提供技術(shù)支持�,有容微電子GM50101:超低附加抖動(dòng)時(shí)鐘緩沖器。

2022-05-07 11:40:15 1071

1071 時(shí)鐘抖動(dòng)使隨機(jī)抖動(dòng)和相位噪聲不再神秘

2022-11-07 08:07:29 4

4 時(shí)鐘抖動(dòng)解秘—高速鏈路時(shí)鐘抖動(dòng)規(guī)范基礎(chǔ)知識(shí)

2022-11-07 08:07:30 1

1 1.1.1.??抖動(dòng)定義和分類(lèi) ITU-T G.701對(duì)抖動(dòng)的定義為:“抖動(dòng)是指數(shù)字信號(hào)在短期內(nèi)相對(duì)于理想位置發(fā)生的偏移重大影響的短時(shí)變化”�。 對(duì)于真實(shí)物理世界中的時(shí)鐘源���,比如晶振、DLL�、PLL���,它們的時(shí)鐘輸出周期都不可能是一個(gè)單點(diǎn)的固定值���,而是隨時(shí)間而變化的

2023-03-10 14:54:32 657

657

系統(tǒng)時(shí)序設(shè)計(jì)中對(duì)時(shí)鐘信號(hào)的要求是非常嚴(yán)格的��,因?yàn)槲覀兯械臅r(shí)序計(jì)算都是以恒定的時(shí)鐘信號(hào)為基準(zhǔn)�。但實(shí)際中時(shí)鐘信號(hào)往往不可能總是那么完美���,會(huì)出現(xiàn)抖動(dòng)(Jitter)和偏移(Skew)問(wèn)題�����。

2023-04-04 09:20:56 1637

1637 首先�����,我們需要理解什么是時(shí)鐘抖動(dòng)。簡(jiǎn)而言之�,時(shí)鐘抖動(dòng)(Jitter)反映的是時(shí)鐘源在時(shí)鐘邊沿的不確定性(Clock Uncertainty)�����。

2023-06-02 09:09:06 1026

1026

先來(lái)聊一聊什么是時(shí)鐘抖動(dòng)��。時(shí)鐘抖動(dòng)實(shí)際上是相比于理想時(shí)鐘的時(shí)鐘邊沿位置�,實(shí)際時(shí)鐘的時(shí)鐘邊沿的偏差�,偏差越大���,抖動(dòng)越大���。實(shí)際上,時(shí)鐘源例如PLL是無(wú)法產(chǎn)生一個(gè)絕對(duì)干凈的時(shí)鐘��。這就意味著時(shí)鐘邊沿出現(xiàn)在

2023-06-09 09:40:50 1128

1128

本文主要介紹了時(shí)鐘偏差和時(shí)鐘抖動(dòng)���。

2023-07-04 14:38:28 960

960

電子發(fā)燒友網(wǎng)站提供《時(shí)鐘抖動(dòng)對(duì)ADC性能有什么影響.pdf》資料免費(fèi)下載

2023-11-28 10:24:10 1

1

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論