多晶硅錠定向凝固生長(zhǎng)方法

鑄錠澆注法是較早出現(xiàn)的一種技術(shù),該方法先將硅料置于熔煉坩堝中加熱熔化,隨后利用翻轉(zhuǎn)機(jī)械將其注入模具內(nèi)....

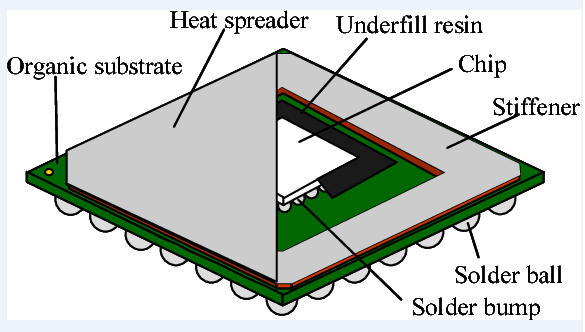

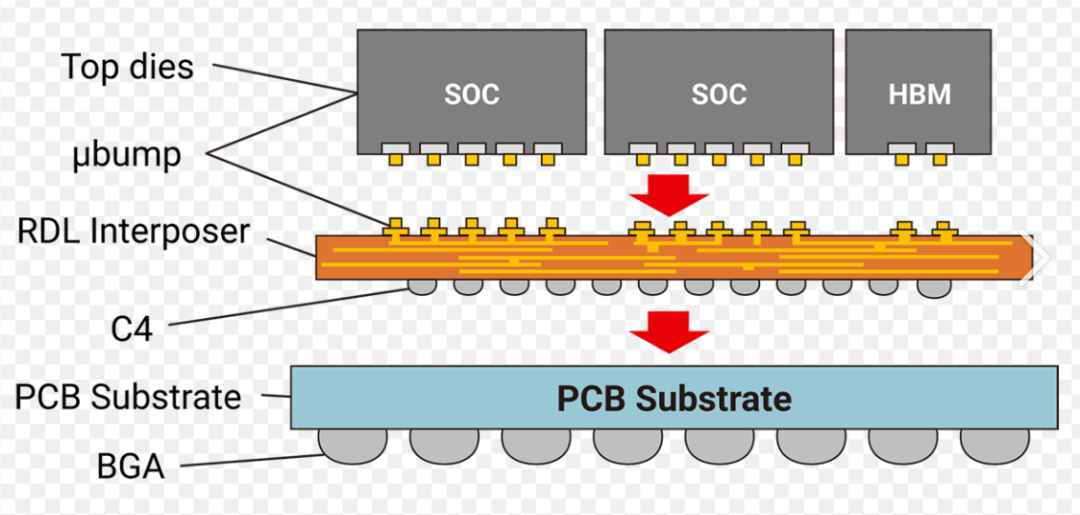

封裝基板設(shè)計(jì)的詳細(xì)步驟

封裝基板設(shè)計(jì)是集成電路封裝工程中的核心步驟之一,涉及將芯片與外部電路連接的基板(substrate)....

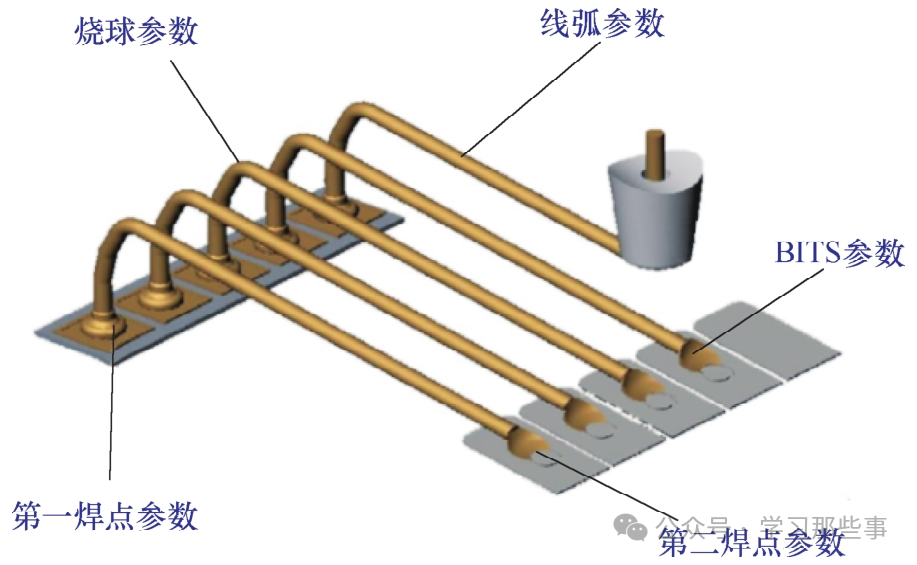

金絲鍵合的主要過程和關(guān)鍵參數(shù)

金絲鍵合主要依靠熱超聲鍵合技術(shù)來(lái)達(dá)成。熱超聲鍵合融合了熱壓鍵合與超聲鍵合兩者的長(zhǎng)處。通常情況下,熱壓....

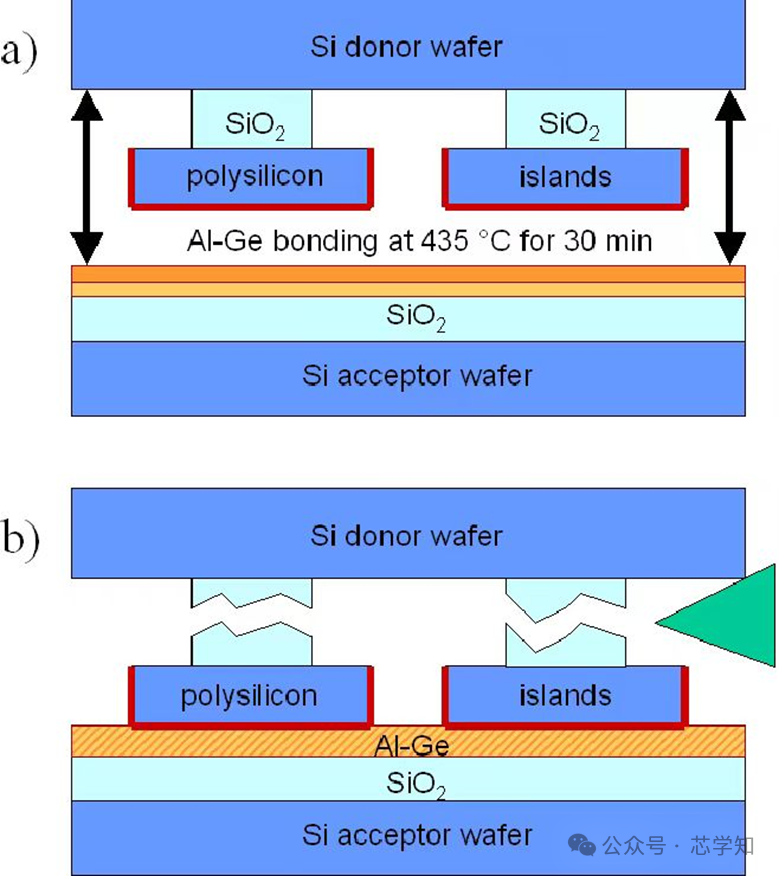

集成電路和光子集成技術(shù)的發(fā)展歷程

本文介紹了集成電路和光子集成技術(shù)的發(fā)展歷程,并詳細(xì)介紹了鈮酸鋰光子集成技術(shù)和硅和鈮酸鋰復(fù)合薄膜技術(shù)。

淺談集成電路設(shè)計(jì)中的標(biāo)準(zhǔn)單元

本文介紹了集成電路設(shè)計(jì)中Standard Cell(標(biāo)準(zhǔn)單元)的概念、作用、優(yōu)勢(shì)和設(shè)計(jì)方法等。

一文詳解淺溝槽隔離技術(shù)

隨著集成電路尺寸縮小至亞微米技術(shù)節(jié)點(diǎn),原始的本征氧化隔離技術(shù)(LocOS)已不適應(yīng)?!案綦x”是指利用....

芯片封裝中的焊點(diǎn)圖案設(shè)計(jì)

Bump Pattern Design(焊點(diǎn)圖案設(shè)計(jì)) 是集成電路封裝設(shè)計(jì)中的關(guān)鍵部分,尤其在BGA....

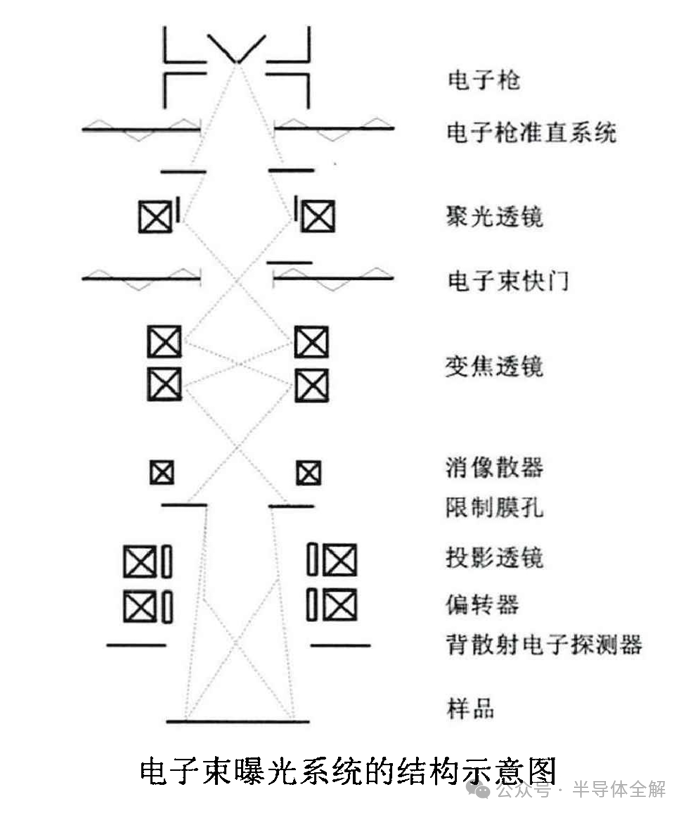

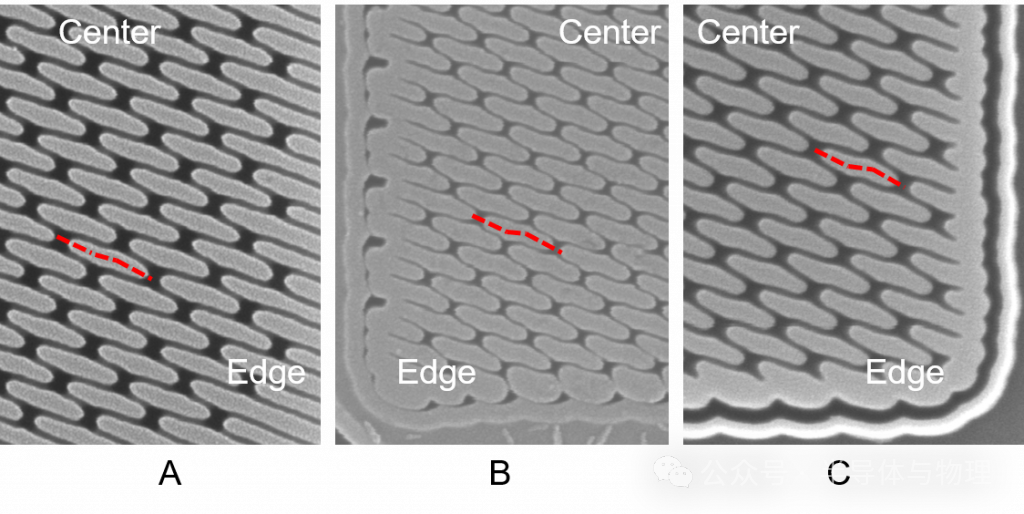

如何進(jìn)行晶圓檢測(cè)

在關(guān)鍵尺寸的在線量測(cè)環(huán)節(jié),所運(yùn)用的設(shè)備主要涵蓋 CD-SEM 以及 OCD(optical crit....

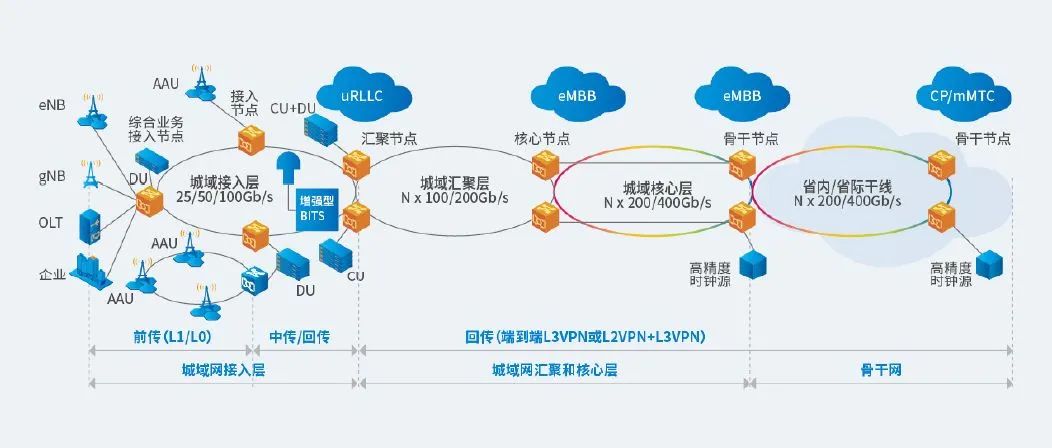

速率可調(diào)的光傳輸和彈性光網(wǎng)絡(luò)

當(dāng)前光纖系統(tǒng)已廣泛應(yīng)用于從接入到核心骨干網(wǎng)的各個(gè)層級(jí)。各層級(jí)因功能需求差異采用不同技術(shù)方案:例如核心....

芯片有源區(qū)的作用和工藝流程

在芯片制造中,有源區(qū)(Active Area)是晶體管的核心工作區(qū)域,負(fù)責(zé)電流的導(dǎo)通與信號(hào)處理。它如....

集成電路封裝設(shè)計(jì)為什么需要Design Rule

封裝設(shè)計(jì)Design Rule 是在集成電路封裝設(shè)計(jì)中,為了保證電氣、機(jī)械、熱管理等各方面性能而制定....

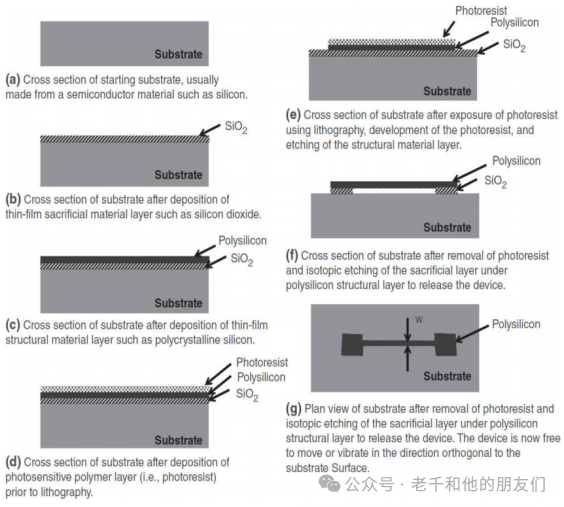

納米技術(shù)的發(fā)展歷程和制造方法

納米技術(shù)是一個(gè)高度跨學(xué)科的領(lǐng)域,涉及在納米尺度上精確控制和操縱物質(zhì)。集成電路(IC)作為已經(jīng)達(dá)到納米....

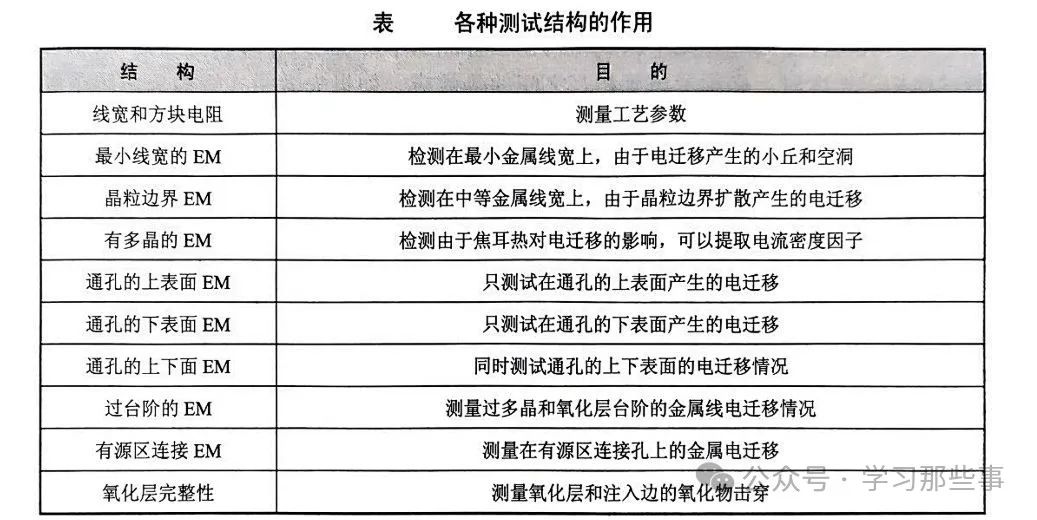

半導(dǎo)體集成電路的可靠性評(píng)價(jià)

半導(dǎo)體集成電路的可靠性評(píng)價(jià)是一個(gè)綜合性的過程,涉及多個(gè)關(guān)鍵技術(shù)和層面,本文分述如下:可靠性評(píng)價(jià)技術(shù)概....

熱管理在芯片封裝中的重要性

如果將芯片封裝比作“房屋結(jié)構(gòu)”,那么熱仿真就像在建造前做“房屋通風(fēng)模擬”。在圖紙階段先預(yù)測(cè)各房間是否....

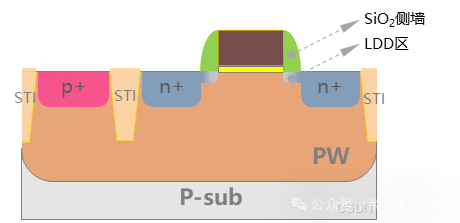

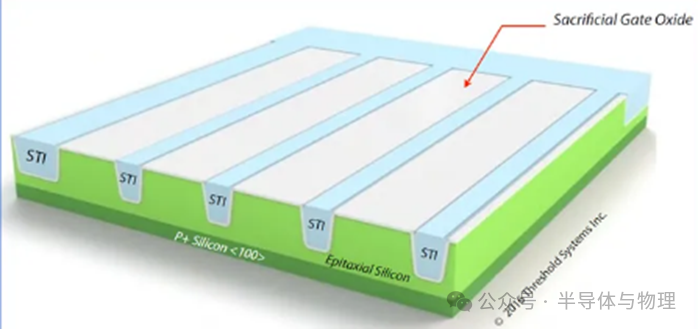

芯片制造中的淺溝道隔離工藝技術(shù)

淺溝道隔離(STI)是芯片制造中的關(guān)鍵工藝技術(shù),用于在半導(dǎo)體器件中形成電學(xué)隔離區(qū)域,防止相鄰晶體管之....

集成電路設(shè)計(jì)與制造過程

一個(gè)復(fù)雜的處理器可能包含數(shù)億甚至數(shù)十(百)億個(gè)晶體管,這些晶體管通過細(xì)金屬線彼此互聯(lián)。芯片的制造過程....

硅集成電路技術(shù)的優(yōu)勢(shì)與挑戰(zhàn)

硅作為半導(dǎo)體材料在集成電路應(yīng)用中的核心地位無(wú)可爭(zhēng)議,然而,隨著科技的進(jìn)步和器件特征尺寸的不斷縮小,硅....

芯片架構(gòu)設(shè)計(jì)的關(guān)鍵要素

芯片架構(gòu)設(shè)計(jì)的目標(biāo)是達(dá)到功能、性能、功耗、面積(FPA)的平衡。好的芯片架構(gòu)能有效提升系統(tǒng)的整體性能....

等離子體蝕刻工藝對(duì)集成電路可靠性的影響

隨著集成電路特征尺寸的縮小,工藝窗口變小,可靠性成為更難兼顧的因素,設(shè)計(jì)上的改善對(duì)于優(yōu)化可靠性至關(guān)重....

集成電路開發(fā)中的器件調(diào)試環(huán)節(jié)

本文介紹了集成電路開發(fā)中的器件調(diào)試環(huán)節(jié),包括其核心目標(biāo)、關(guān)鍵技術(shù)與流程等內(nèi)容。